<BR>`timescale 1ns / 1ps<BR>//////////////////////////////////////////////<BR>// 2's Complement, Absolute Unit Design<BR>//////////////////////////////////////////////<BR><BR>//2's Complement Unit<BR>module twos_com(ref_data_8bit,com_out);<BR> input [7:0] ref_data_8bit; // 8bit input unsigned number<BR> output [15:0] com_out; // 16bit output signed number<BR><BR> // 8bit input is 1's complement -> +1 => 2's complement<BR> // and then 8bit is extend to 16bit<BR> assign com_out = {11111111, ~ref_data_8bit+1};<BR>endmodule<BR><BR>// Absolute Unit<BR>module abs_mode(abs_in, abs_out);<BR> input [9:0] abs_in; // absolute unit input 10bit<BR> output [9:0] abs_out; // absolute unit output 10bit<BR><BR> //if abs_in MSB is '0' then abs_in = positive<BR> // abs_in MSB is '1' then abs_in = negative<BR> assign abs_out = abs_in[9]?~(abs_in-1):abs_in;<BR>endmodule<BR>

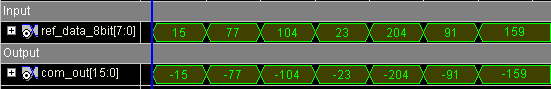

2의 보수를 만드는 Unit의 경우 부호가 없는 8bit의 데이터를 입력받은 후

1의 보수를 취하기 위해 ~ 연산을 수행하였다.

그 뒤에 1을 더하여 2의 보수를 구하고 그 결과를 16bit로 확장하기 위해 { 비트1, 비트2 }로 묶었다.

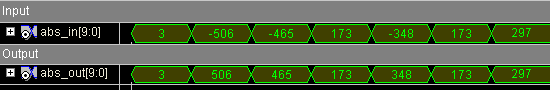

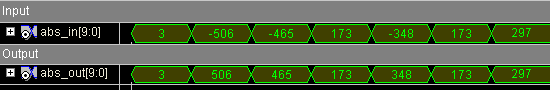

절대값을 취하는 Unit의 경우 입력받은 데이터는 10bit의 signed number이다.

따라서 입력한 bit가 양수인지 음수인지 파악하기 위해 최상위 비트(MSB)값에 대한 조건문을 추가한다.

그 값이 참일 경우 음수임을 의미하므로, 1을 빼고 1의 보수를 취해서 양수로 만들어준다.

MSB가 0인 경우 양수이므로, 입력받은 데이터를 그대로 출력한다.

< 2’s Complement Unit Simulation Result >

< Absolute Unit >

< Absolute Unit >

< Test Bench > < Absolute Unit >

< Absolute Unit >[#M_ more.. | less.. |

<BR>`timescale 1ns / 1ps /////////////////////////////////////////////////////<BR>// 2's Complement, Absolute Unit Design Test Bench<BR>// 200420174 Jeon Chang Kyu<BR>/////////////////////////////////////////////////////<BR>module twos_com_tb_v;<BR> // Inputs<BR> reg [7:0] ref_data_8bit;<BR> // Outputs<BR> wire [15:0] com_out;<BR><BR> // 2's complement unit: U1<BR> twos_com U1 (.ref_data_8bit(ref_data_8bit), .com_out(com_out));<BR><BR> initial begin<BR> ref_data_8bit = 8'b00001111; #50; //50ns delay<BR> ref_data_8bit = 8'b01001101; #50; //50ns delay<BR> ref_data_8bit = 8'b01101000; #50; //50ns delay<BR> ref_data_8bit = 8'b00010111; #50; //50ns delay<BR> ref_data_8bit = 8'b11001100; #50; //50ns delay<BR> ref_data_8bit = 8'b01011011; #50; //50ns delay<BR> ref_data_8bit = 8'b10011111;<BR> end<BR>endmodule<BR><BR>module abs_mode_tb_v;<BR> // Inputs<BR> reg [9:0] abs_in;<BR> // Outputs<BR> wire [9:0] abs_out;<BR><BR> // Absolute unit: U2<BR> abs_mode U2 (.abs_in(abs_in),.abs_out(abs_out));<BR><BR> initial begin<BR> abs_in = 10'b0000000011; #50; //50ns delay<BR> abs_in = 10'b1000000110; #50; //50ns delay<BR> abs_in = 10'b1000101111; #50; //50ns delay<BR> abs_in = 10'b0010101101; #50; //50ns delay<BR> abs_in = 10'b1010100100; #50; //50ns delay<BR> abs_in = 10'b0010101101; #50; //50ns delay<BR> abs_in = 10'b0100101001;<BR> end<BR>endmodule<BR>

_M#]