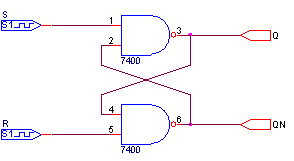

< R-S Latch 회로 >

< R-S Latch 회로 > < R-S Latch 출력 파형 >

< R-S Latch 출력 파형 >위 출력에서 주의깊게 봐야할 부분은 처음 부분으로,

R과 S가 모두 ‘0’이면 Q와 QN 모두 ‘1’이 된다는 사실이다.

그리고, ’00’에서 ’11’로 바뀌게 되면 metastable 상태가 된다.

====================================================================

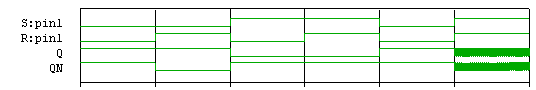

< R-S Flip-flop with Clock Input 회로 >

< R-S Flip-flop with Clock Input 회로 > < R-S Flip-flop with Clock Input 출력 파형 >

< R-S Flip-flop with Clock Input 출력 파형 >CLK은 DigClock 소자를 사용하고, 기타 다른 입력은 Stim1을 사용

====================================================================

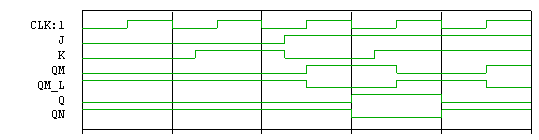

< Master-slave Clocked J-K Flip-flop 회로 >

< Master-slave Clocked J-K Flip-flop 회로 > < Master-slave Clocked J-K Flip-flop 출력 파형 >

< Master-slave Clocked J-K Flip-flop 출력 파형 >* 참고: http://en.wikipedia.org/wiki/Latch_(electronics)

http://en.wikipedia.org/wiki/Flip-flop_(electronics)

metastable 상태가 무엇이지요?? 제가 전기전자에 관심이 많아서 RS플립플롭을 공부하고있는데…궁금해서요

좋아요좋아요

metastable의 의미 자체는 준안정입니다. 출력이 ‘1’이 될 지, ‘0’이 될 지 결정할 수 없는 상황을 의미합니다. RS-F/F을 예로 들면 R과 S가가 모두 ‘0’이면 출력은 모두 ‘1’이 됩니다. 이 때 출력을 어떤 순서로 계산하는지에 따라 결과가 다릅니다. 이와 같이 출력을 예측할 수 없는 경우를 말합니다.

좋아요좋아요

감사합니다^^

좋아요좋아요